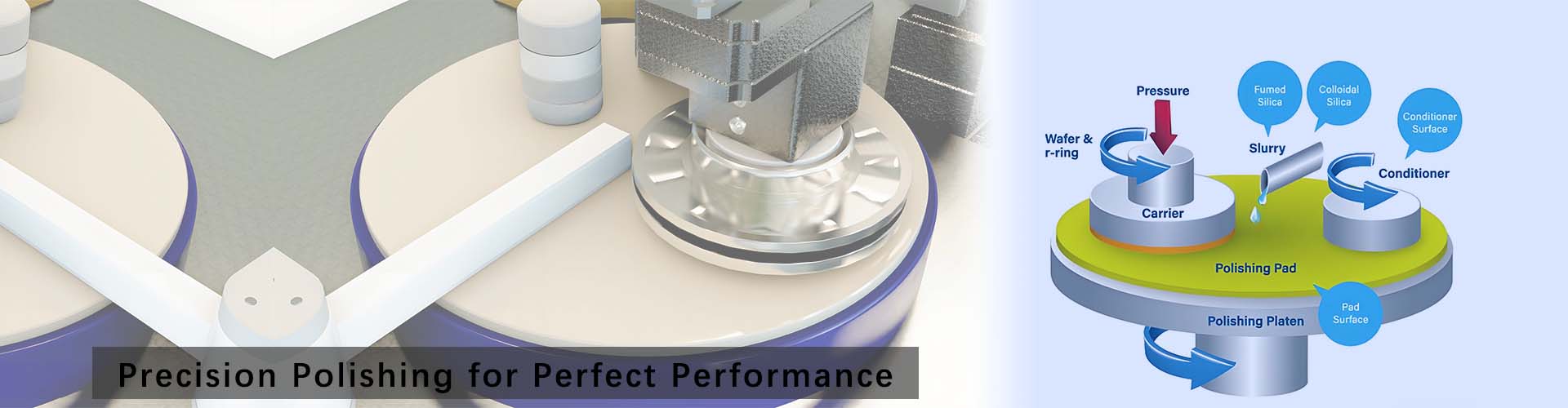

I. Como equipo clave en la fabricación de semiconductores, la precisión de procesamiento de

las máquinas de pulido de wafers determina directamente el rendimiento de los chips. Actualmente, aún enfrentan múltiples cuellos de botella técnicos en la consecución de índices de ultr precisión y el control de estabilidad, que requieren avances a través de innovaciones técnicas multidimensionales.